HYMEX: Energy-Efficient HYbrid MEmory based Architecture for NeXt-Generation AI Systems

This page is under preparation. Please visit this page to have an early peak at the project.

Links: [JSPS Grants-in-Aid for Scientific Research] / [University of Aizu] / [PI's Researchmap] / [Project Database] / [Project Page]

Information

- Funder: KAKENHI (Grant-in-Aid for Scientific Research B)

- Project No: 26K02883

- Duration: 2026/04-2029/03

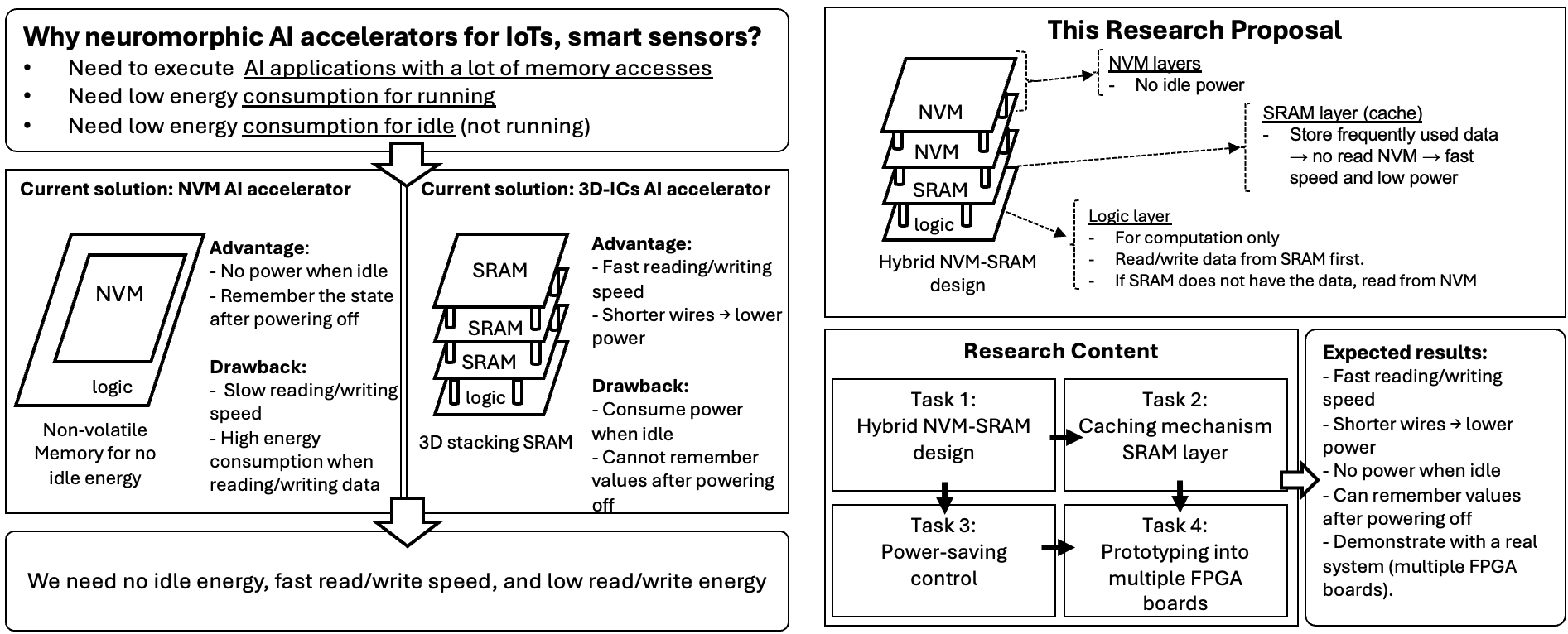

- Summary: Artificial Intelligence (AI) has made great progress, but its high energy consumption remains a serious challenge, especially for small devices such as smartphones, IoT sensors, and battery- or solar-powered systems. This project proposes a new energy-efficient neuromorphic AI accelerator using 3D integrated circuits (3D-ICs) that combine Non-Volatile Memory (NVM) and SRAM to reduce power usage both during operation and idle periods. NVM can retain data without power, significantly lowering idle energy consumption, but it is typically slower and more energy-intensive during read/write operations than SRAM. To address this, we introduce a hybrid memory architecture in which stacked NVM layers are placed above the logic layer to shorten data transfer distance, while a small, fast SRAM layer acts as a cache between logic and NVM to improve speed and reduce read/write energy. In addition, adaptive power management techniques dynamically adjust energy usage based on available power with minimal impact on accuracy and performance. With these technologies, the proposed design aims to reduce energy consumption during operation and during idle time, enabling practical low-power AI chips for real-world applications such as smartphones, IoT devices, and smart sensors.

Research Technology & Prototyping

Our research group specializes in the design and validation of high-efficiency AI hardware and next-generation memory-compute systems. We leverage industry-leading AMD (formerly Xilinx) FPGA platforms to bridge the gap between architectural theory and physical silicon realization.

Core Methodologies

Full-System Prototyping: We utilize a rigorous RTL-based design flow (Verilog/VHDL) within the Vivado™ and Vitis™ environments. This ensures cycle-accurate hardware validation and reliable performance benchmarking for complex neural accelerators.

3D-IC & Interconnect Emulation: Recognizing the challenges of iterative 3D-IC fabrication, we use advanced Programmable Network-on-Chip (NoC) features to simulate high-bandwidth vertical interconnects and through-silicon via (TSV) latency characteristics.

Advanced Memory Modeling: Our group develops custom behavioral wrappers to model the timing, energy signatures, and data-retention properties of emerging technologies, such as Non-Volatile Memory (NVM) and high-density 3D-stacked SRAM.

By using adaptive computing platforms as high-fidelity emulation vehicles, we can explore innovative architectural trade-offs—such as Memory–Compute Co-Design and Event-Driven AI—with the precision of hardware-level execution. This methodology allows us to accelerate the development cycle for low-power AI chips targeting edge devices, smartphones, and autonomous IoT sensors.

Open Source

The final program will be released in Github under MIT license in the future.

Team Members

Students

AY2026

- HANYU Yuga

- SHARMA Atharv

- LUYEN Van-Vu

- KOMATSUZAKI Aruki

Schedule

Early Prototyping (Prior AY2026)

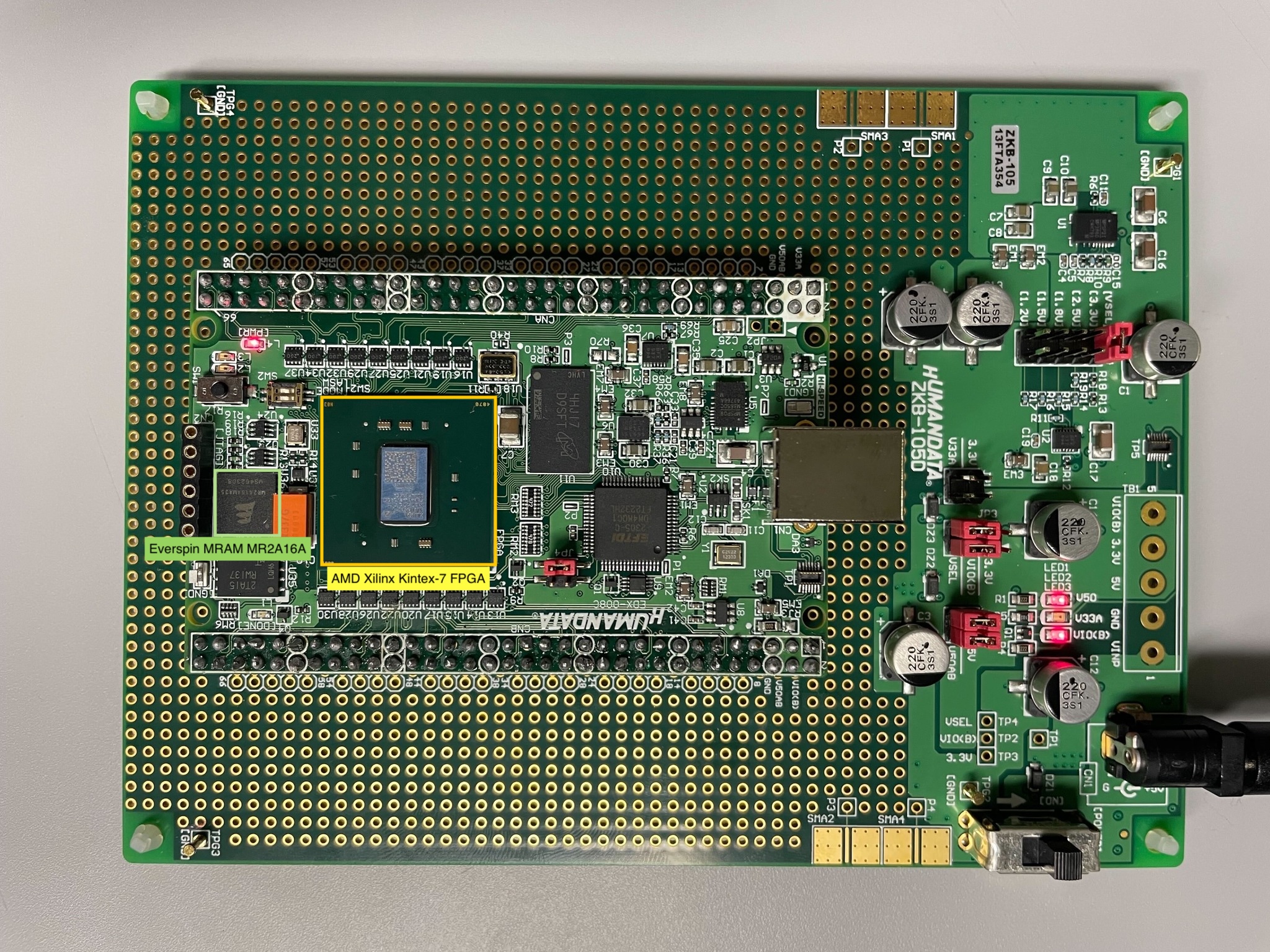

As a early prototyping, we use HumanDATA Kintex 7 EDX-008-70T to validate the read/write of MRAM by Everspin.

Overall schedule

Meeting

AY2026

| Date | Meeting | Minutes |

|---|---|---|

| 2026-04-13 | Project Kickoff | Discussed scope and timeline |

| 2026-04-27 | Bi-Weekly Sync |

Contact

- khanh [at] u-aizu.ac.jp